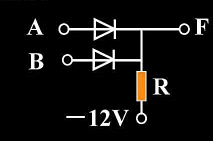

更多“已知两个输入端AB的波形,试画出输出波形。”相关的问题

更多“已知两个输入端AB的波形,试画出输出波形。”相关的问题

第1题

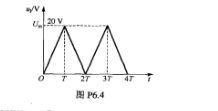

已知由555定时器构成的施密特触发器的输入波形如图P6.4所示.其中,Um=20v,电源电压VDD=

18V,定时器控制端CO通过电容接地,试画出施密特触发器对应的输出波形.如果定时器控制端CO外按控制电压Us=16V时,试画出施密特触发器对应的输出波形.

点击查看答案

第2题

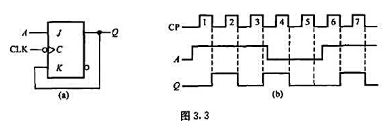

JK触发器组成图3.3(a)所示电路.试分析电路的逻辑功能.已知电路CLK和A的输入波形如图3.3(b)所示

JK触发器组成图3.3(a)所示电路.试分析电路的逻辑功能.已知电路CLK和A的输入波形如图3.3(b)所示.设Q输出初态为0,画出Q的波形.

第3题

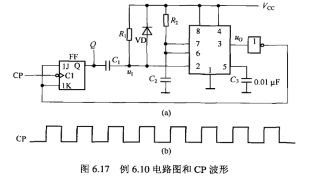

由主从JK触发器和555定时器组成的电路如图6.17(a)所示.已知CP为10Hz的方波,如图6.17(b)所示.R

由主从JK触发器和555定时器组成的电路如图6.17(a)所示.已知CP为10Hz的方波,如图6.17(b)所示.R1=10kΩ、R2=56kΩ、C1=1000pF、C2=4.7uF,触发器Q端及555输出端(3端)初态均为“0".

(1)试画出Q端,u1、uO相对于CP脉冲的波形.

(2)试求Q端输出波形的周期.

第4题

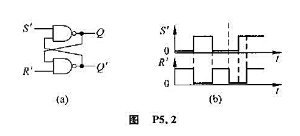

画出图P5.2(a)中SR锁存器输出端Q和Q'的电压波形。输入端S'和R'的电压波形如图P5.2(b)

画出图P5.2(a)中SR锁存器输出端Q和Q'的电压波形。输入端S'和R'的电压波形如图P5.2(b)所示。

第5题

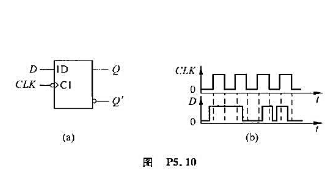

画出图P5.10(a)中边沿触发D触发器输出端Q和Q'的电压波形。时钟脉冲CLK和输入端D的电压波形如

画出图P5.10(a)中边沿触发D触发器输出端Q和Q'的电压波形。时钟脉冲CLK和输入端D的电压波形如图P5.10(b)所示。设触发器的初始状态为Q=0。

第8题

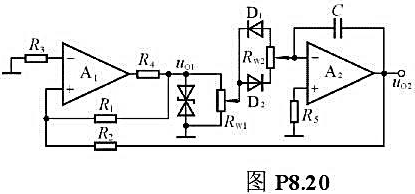

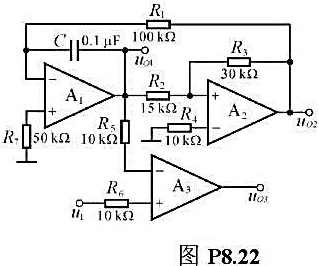

电路如图P8.22所示,已知集成运放的最大输出电压幅值为±12V,uI的数值在uo1的峰一峰值之间.

(1)求解uo3的占空比与u1的关系式;

(2)设u1=2.5V,画出uo1、uo2和uo3的波形.

第9题

已知f(t)=t[u(t)-u(t-1)],求s(t)=f(t)*f(t),并画出s(t)的波形。

已知f(t)=t[u(t)-u(t-1)],求s(t)=f(t)*f(t),并画出s(t)的波形。

点击查看答案

第11题

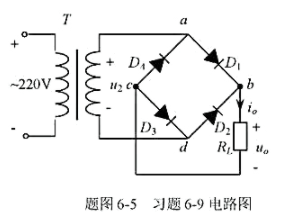

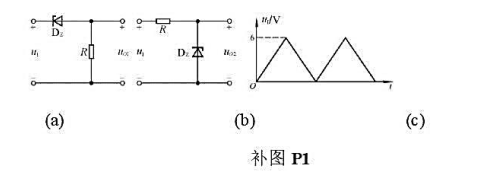

电路如补图P1(a)、(b)所示,稳压管的稳定电压Uz=3V,R的取值合适,uI的波形如图(c)所示.试

电路如补图P1(a)、(b)所示,稳压管的稳定电压Uz=3V,R的取值合适,uI的波形如图(c)所示.试分别画出uo1和uo2的波形.

如果结果不匹配,请

如果结果不匹配,请