更多“数字触发器在某一时刻的输出状态,不仅取决于当时的输入信号的状…”相关的问题

更多“数字触发器在某一时刻的输出状态,不仅取决于当时的输入信号的状…”相关的问题

第3题

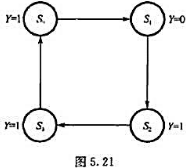

图5.21表示一个时序状态机的状态转换图.该状态机有四个状态,在时钟作用下,状态机在四个状态之

图5.21表示一个时序状态机的状态转换图.该状态机有四个状态,在时钟作用下,状态

机在四个状态之间轮流转换.状态机的状态由A、B两个寄存器(触发器)定义:当A=0,B=1时,输出信号Y=0;其余A、B组合情况下,输出Y均为1.

用ISP器件设计该时序状态机,写出VHDL源文件.

第5题

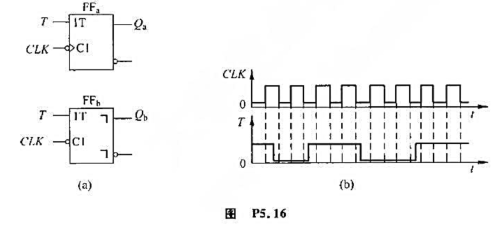

画出图P5.16(a)中触发器FF1和FF2的输出Q1和Q2的电压波形。已知CLK及T的电压波形

画出图P5.16(a)中触发器FF1和FF2的输出Q1和Q2的电压波形。已知CLK及T的电压波形

点击查看答案

如图P5.16(b)所示。设触发器的初始状态均为Q=0。

第6题

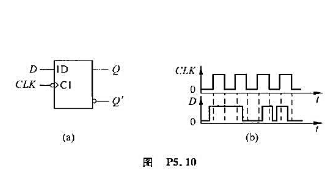

画出图P5.10(a)中边沿触发D触发器输出端Q和Q'的电压波形。时钟脉冲CLK和输入端D的电压波形如

画出图P5.10(a)中边沿触发D触发器输出端Q和Q'的电压波形。时钟脉冲CLK和输入端D的电压波形如图P5.10(b)所示。设触发器的初始状态为Q=0。

第7题

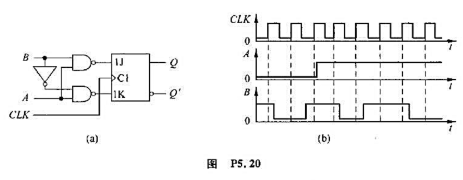

写出图P5.20(a)电路中触发器次态Q'与现态Q和A、B之间关系的逻辑函数式,并画出在图P5.20(b)给

写出图P5.20(a)电路中触发器次态Q'与现态Q和A、B之间关系的逻辑函数式,并画出在图P5.20(b)给定的输入电压波形下触发器输出的电压波形。设触发器的初始状态为Q=0。

如果结果不匹配,请

如果结果不匹配,请