更多“试比较继电器梯形图、逻辑功能图、功能流程图有什么联系和区别?”相关的问题

更多“试比较继电器梯形图、逻辑功能图、功能流程图有什么联系和区别?”相关的问题

第2题

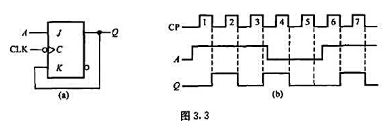

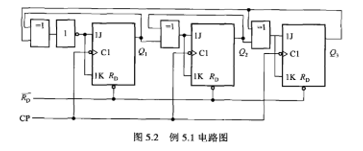

JK触发器组成图3.3(a)所示电路.试分析电路的逻辑功能.已知电路CLK和A的输入波形如图3.3(b)所示

JK触发器组成图3.3(a)所示电路.试分析电路的逻辑功能.已知电路CLK和A的输入波形如图3.3(b)所示.设Q输出初态为0,画出Q的波形.

第5题

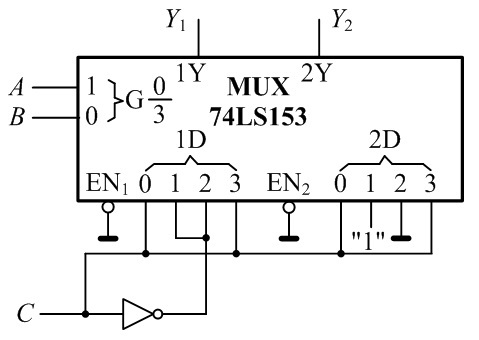

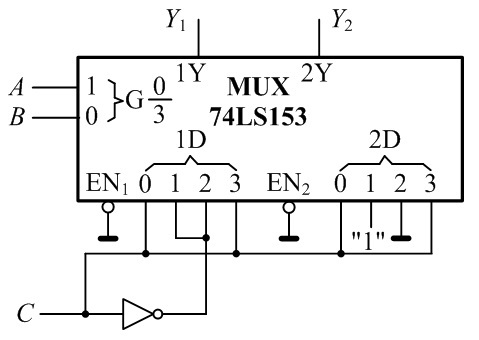

用双4选1数据选择器74LS153实现的逻辑电路如下图所示,试分析该电路的逻辑功能,下列说法正确的是()。

A.该电路实现全加器的逻辑功能,Y1为和的输出,Y2为进位输出

B.该电路实现一致性判别的逻辑功能,Y1是判别为一致时的输出,Y2为不一致的输出

C.该电路实现奇偶校验的逻辑功能,Y1为奇数输出,Y2为偶数输出

D.该电路实现全减器的逻辑功能,Y1为差的输出,Y2为借位输出

第6题

以下对结构化开发方法描述不正确的是 A 以代表问题领域的对象为中心 B 程序编写方式是处理

以下对结构化开发方法描述不正确的是

A 以代表问题领域的对象为中心

B 程序编写方式是处理流程;封装方式程序模块 C 系统设计是定义模块、函数、流程、物理数据D 需求分析是描述模块功能、函数逻辑、数据字典

第8题

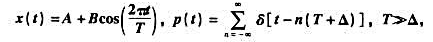

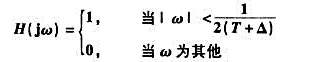

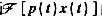

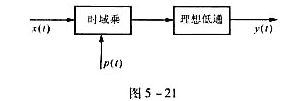

图5-21所示抽样系统理想低通系统函数表达式为输出端可得到,其中a<1,k为实系数.求:(1)画的图形

图5-21所示抽样系统理想低通系统函数表达式为输出端可得到,其中a<1,k为实系数.求:(1)画的图形

点击查看答案

图5-21所示抽样系统

理想低通系统函数表达式为

输出端可得到 ,其中a<1,k为实系数.求:

,其中a<1,k为实系数.求:

(1)画 的图形;

的图形;

(2)为实现上述要求给出A取值范围;

(3)求at求k;

(4)此系统在电子测量技术中可构成抽样(采样)示波器,试说明此种示波器的功能特点.

第10题

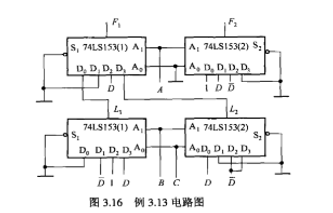

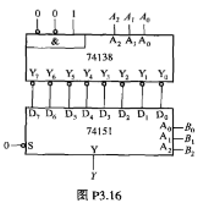

图3.16所示逻辑电路所用器件为74LS153(双4选1多路开关),试列出F1,F2的逻辑函数表达式

图3.16所示逻辑电路所用器件为74LS153(双4选1多路开关),试列出F1,F2的逻辑函数表达式

点击查看答案

,并求其最简与或表达式.

第11题

在图10.2.7所示逐次比较A/D转换器中设VREF=10V,vi=8.26V,试画出在时钟脉冲作用下,v

在图10.2.7所示逐次比较A/D转换器中设VREF=10V,vi=8.26V,试画出在时钟脉冲作用下,v'0的波形并写出转换结果。

如果结果不匹配,请

如果结果不匹配,请

时的图象.

时的图象.