题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

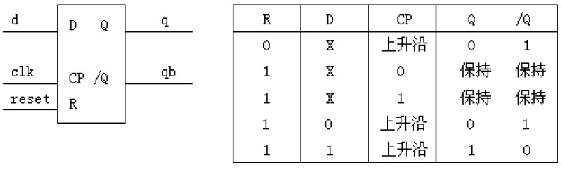

用VHDL语言描述带同步置位/复位端的D触发器(如图3-5所示,真值表如表3-3所示)的逻辑功能。 表3-3

用VHDL语言描述带同步置位/复位端的D触发器(如图3-5所示,真值表如表3-3所示)的逻辑功能。

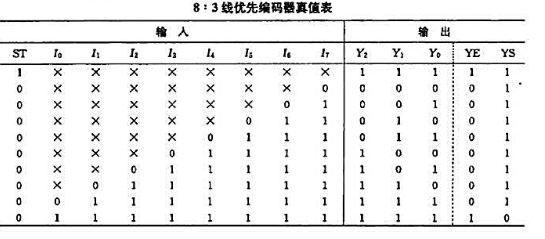

| 表3-3 带同步置位/复位端的D触发器的真值表 | |||||

| S | R | D | CLK | Q | Q' |

| 0 1 1 1 1 | 1 0 1 1 1 | × × × 0 1 | 上升沿 上升沿 0 上升沿 上升沿 | 1 0 保持 0 1 | 0 1 保持 1 0 |

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“用VHDL语言描述带同步置位/复位端的D触发器(如图3-5所…”相关的问题

更多“用VHDL语言描述带同步置位/复位端的D触发器(如图3-5所…”相关的问题