题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

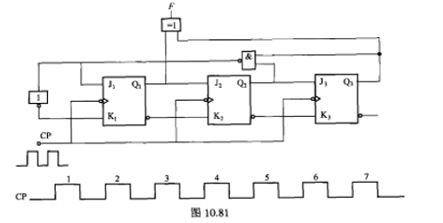

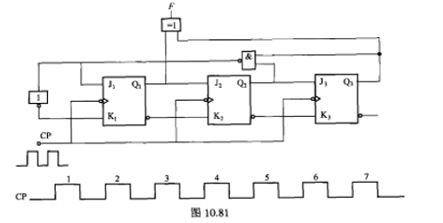

逻辑线路如图10.81所示,当连续输入7个正CP脉冲时,画出Q1、Q2、Q3和F的对应波形.(各

逻辑线路如图10.81所示,当连续输入7个正CP脉冲时,画出Q1、Q2、Q3和F的对应波形.(各

触发器起始均为0态)

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

触发器起始均为0态)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“逻辑线路如图10.81所示,当连续输入7个正CP脉冲时,画出…”相关的问题

更多“逻辑线路如图10.81所示,当连续输入7个正CP脉冲时,画出…”相关的问题

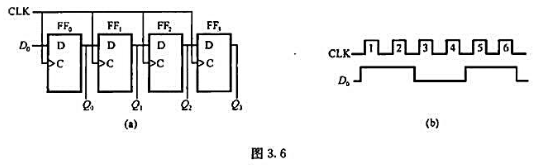

移位寄存器的逻辑结构图如图3.6(a)所示,CLK和D0的输入波形如图3.6(b)所示.设Q初始状态为0,画出Q3~Q0的波形.

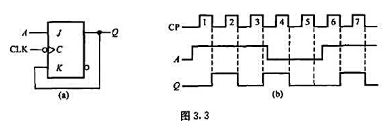

JK触发器组成图3.3(a)所示电路.试分析电路的逻辑功能.已知电路CLK和A的输入波形如图3.3(b)所示.设Q输出初态为0,画出Q的波形.

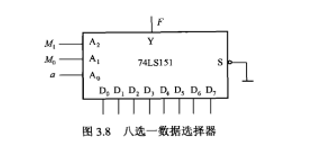

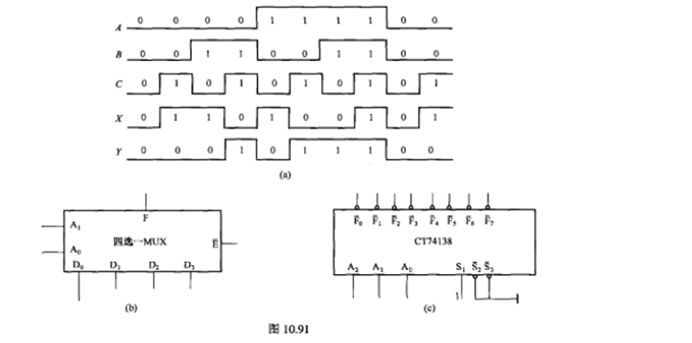

逻辑功能,并分别用基本逻辑门电路、四选一MUX数据选择器(如图10.91(b))和3-8译码器(如图10.91(c))实现此逻辑电路.

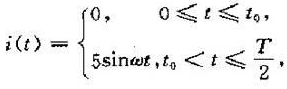

某可控硅控制线路中,流过负载R的电流i(t)如图6-21所示,即

其中l0称为触发时间,如果T=0.02(s)(即ω= =100π)

=100π)

(1)当触发时间t0=0.0025(s)时,求0≤t≤ 内电流的平均值;

内电流的平均值;

(2)当触发时间为t0时,求[0, ]内电流的平均值;

]内电流的平均值;

(3)要使i平均= (A)和

(A)和 (A),问相应的触发时间应为多少?

(A),问相应的触发时间应为多少?

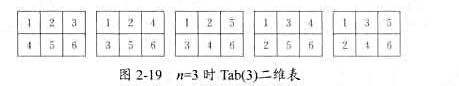

算法设计:给定正整数n,计算Tab(n)中2xn的标准二维表的个数.

数据输入:由文件input.txt给出输入数据.第1行有1个正整数n.

结果输出:将计算出的Tab(n)中2xn的标准:二维表的个数输出到文件output.txt.