更多“电路如图,所用器件为4选1数据选择器。 写出四选一数据选择器…”相关的问题

更多“电路如图,所用器件为4选1数据选择器。 写出四选一数据选择器…”相关的问题

第2题

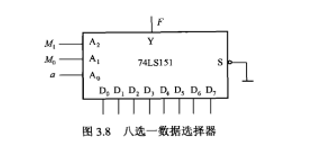

设计一个多功能组合逻辑电路,M1、M0为多功能选择输入信号,a、b为逻辑变量,F为电路的输出

,当M1M0取不同值时,电路具有不同的逻辑功能如表3.9所示.试用八选一数据选择器和最少的与非门实现,规定M1、M0及a分别接选择器的A2A1A0如图3.8所示.

点击查看答案

第3题

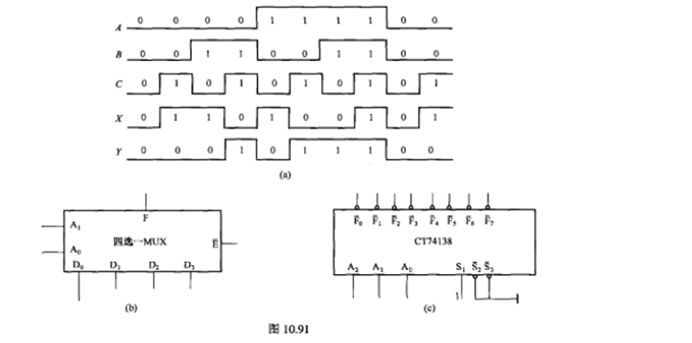

电路的输入A、B、C和输出X、Y的波形如图10.91(a)所示,列出真值表,写出表达式,化简为最简式,分析其

电路的输入A、B、C和输出X、Y的波形如图10.91(a)所示,列出真值表,写出表达式,化简为最简式,分析其

点击查看答案

逻辑功能,并分别用基本逻辑门电路、四选一MUX数据选择器(如图10.91(b))和3-8译码器(如图10.91(c))实现此逻辑电路.

第4题

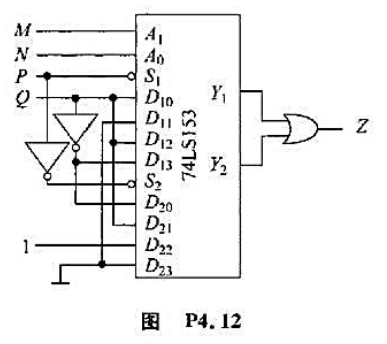

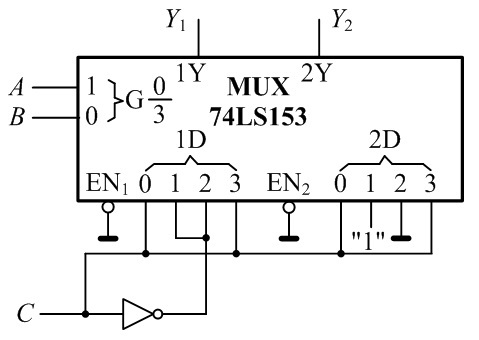

用双4选1数据选择器74LS153实现的逻辑电路如下图所示,试分析该电路的逻辑功能,下列说法正确的是()。

A.该电路实现全加器的逻辑功能,Y1为和的输出,Y2为进位输出

B.该电路实现一致性判别的逻辑功能,Y1是判别为一致时的输出,Y2为不一致的输出

C.该电路实现奇偶校验的逻辑功能,Y1为奇数输出,Y2为偶数输出

D.该电路实现全减器的逻辑功能,Y1为差的输出,Y2为借位输出

第5题

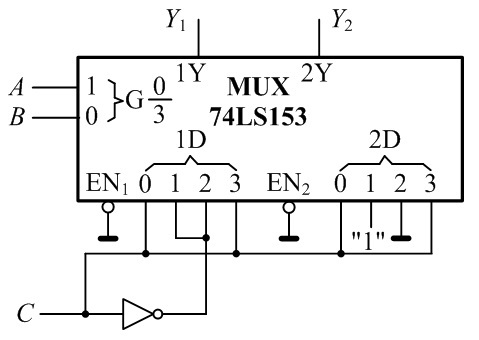

图3.16所示逻辑电路所用器件为74LS153(双4选1多路开关),试列出F1,F2的逻辑函数表达式

图3.16所示逻辑电路所用器件为74LS153(双4选1多路开关),试列出F1,F2的逻辑函数表达式

点击查看答案

,并求其最简与或表达式.

第9题

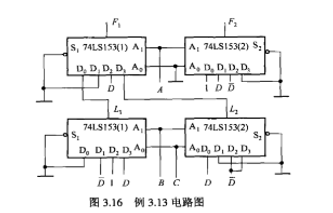

图3.18(a)是一种序列信号发生器电路,它由一个计数器和一个四选一数据选择器构成.分析计数器的

图3.18(a)是一种序列信号发生器电路,它由一个计数器和一个四选一数据选择器构成.分析计数器的工作原理,确定其模值和状态转换关系,确定在计数器输出控制下,数据选择器的输出序列.

第11题

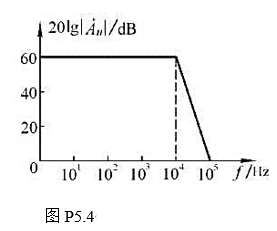

已知某电路的幅频特性如图P5.4所示,试问:(1)该电路的耦合方式;(2)该电路由几级放大电路组成;(3

已知某电路的幅频特性如图P5.4所示,试问:(1)该电路的耦合方式;(2)该电路由几级放大电路组成;(3)当f=104Hz时,附加相移为多少?当f=105Hz时,附加相移又约为多少?(4)该电路的上限频率fg为多少?

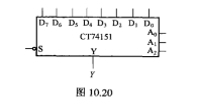

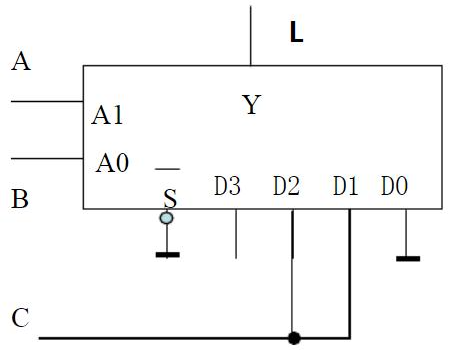

写出四选一数据选择器的输出逻辑表达式。

写出四选一数据选择器的输出逻辑表达式。

如果结果不匹配,请

如果结果不匹配,请