题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

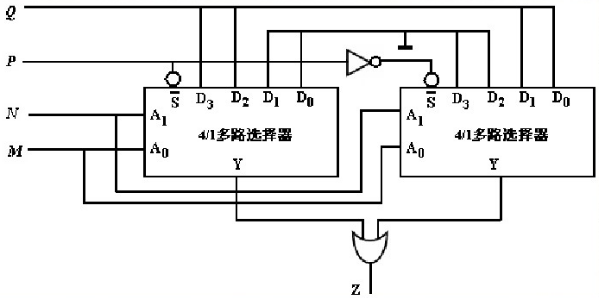

图4.17是用两个4选1数据选择器组成的逻辑电路,试写出输出Z与输入M、N、P、Q之间的逻辑函数式。已知数据选择器的

逻辑函数式为

Y=[D0A'1A'0+D1A'1A0+D2A1A'0+D3A1A0]S

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

逻辑函数式为

Y=[D0A'1A'0+D1A'1A0+D2A1A'0+D3A1A0]S

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“图4.17是用两个4选1数据选择器组成的逻辑电路,试写出输出…”相关的问题

更多“图4.17是用两个4选1数据选择器组成的逻辑电路,试写出输出…”相关的问题

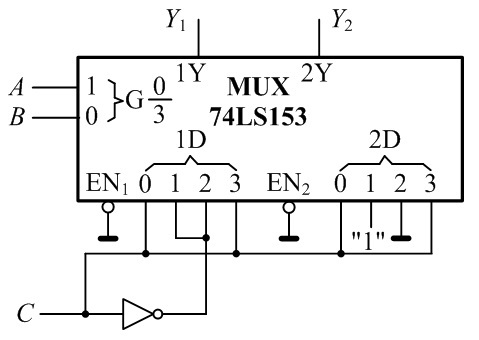

试用给定的双4选1数据选择器74LS153及其他门电路设计一个两位二进制数比较电路。设输入A=A1A0,B=B1B0。输出为A>B、A<B及A=B三种情况且要求输出低电平有效。

A.该电路实现全加器的逻辑功能,Y1为和的输出,Y2为进位输出

B.该电路实现一致性判别的逻辑功能,Y1是判别为一致时的输出,Y2为不一致的输出

C.该电路实现奇偶校验的逻辑功能,Y1为奇数输出,Y2为偶数输出

D.该电路实现全减器的逻辑功能,Y1为差的输出,Y2为借位输出

用双四选一数据选择器74LS153(如图3.2.29所示)设计一个四变量的多数表决电路。当输入变量A、B、C、D有3个或3个以上为1时,输出为1,否则输出为0。

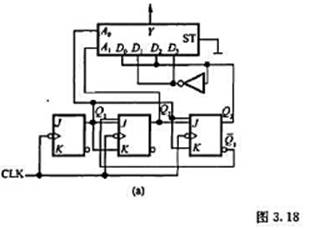

图3.18(a)是一种序列信号发生器电路,它由一个计数器和一个四选一数据选择器构成.分析计数器的工作原理,确定其模值和状态转换关系,确定在计数器输出控制下,数据选择器的输出序列.